Вопросы по теме 'verilog'

Почему этот код Verilog не компилируется?

Часть, которая вызывает проблемы, это c[1] = p[0] + g[0] & c0; . Что с этим не так?

module CLA_gen(p, g, c0, c);

input [3:0] p;

input [3:0] g;

input c0;

output reg [4:1] c;

begin

c[1] = p[0] + g[0] & c0;

end

endmodule

07.11.2023

Verilog несколько одновременных независимых назначений сигналов в тестовой среде

В VHDL я могу написать это в своем тестовом стенде:

signal clk : std_logic := '0';

signal count_in : std_logic_vector(3 downto 0) := "0000";

signal load : std_logic := '0';

signal reset : std_logic := '0';...

21.01.2024

6-битный двоичный счетчик со светодиодным выходом

Я действительно новичок в мире Verilog, и я не могу понять, почему моя программа ничего не возвращает. Я пытаюсь сделать простой 6-битный счетчик, который рассчитывается при нажатии кнопки. Код

module top (CLK, BTN_RST, LED, BTN_C);

input...

16.01.2024

Xilinx Verilog `определить макрос для замены имени провода/рег.

Мы пытаемся сделать что-то вроде следующего в verilog:

`define MY_SUFFIX suffix

wire prefix_`MY_SUFFIX;

assign prefix_`MY_SUFFIX = 1'b0;

Однако препроцессор, похоже, не выполняет правильную замену. Есть синтаксическая ошибка в строке assign...

26.12.2023

Полная сумма сумматора отключена на один тактовый цикл

Я тестирую функциональность 8-битного сумматора Ripple Carry Adder с помощью тестового стенда, который пробует каждую комбинацию. По какой-то причине сумма текущих значений A и B вычисляется в следующем такте. Я не уверен, почему это происходит....

08.12.2023

Два генвара в одном генарте за цикл?

Приведенный ниже вид цикла генерации действителен в системе verilog.

genvar i,j;

for (i=0,j=5; i<5 && j<10; i++,j++) begin:M1

integer t;

initial begin

t = i*j;

end

endgenerate

28.12.2023

Verilog, не может генерировать битовый поток

Первый раз в Vivado Verilog здесь, я только что закончил кодирование для проекта и моделирование для проекта. Я продолжаю получать сообщение об ошибке при попытке сгенерировать битовый поток... Я думаю, что мой синтаксис правильный, просто не могу...

11.01.2024

Передача параметров между модулями Verilog

Я довольно новичок в Verilog и изучаю веревки. У меня есть код, который генерирует 8-битный счетчик вверх (модуль counter.v ), который затем вызывается верхним модулем ( top_module.v ). Существует тестовая фикстура моделирования ( test_fixture.v ),...

18.01.2024

Почему в этом коде логический сдвиг вправо ведет себя как арифметический сдвиг вправо?

Я создаю модуль сумматора с плавающей запятой, и часть его требует 2-х дополнительных и сдвигающих значений. Код основного модуля

module backup (x, y, z, clk);

input [7:0] x,y;

output reg [7:0] z;

input clk;

integer i;

reg [1:0] a;

reg unsigned...

06.11.2023

Ошибка моделирования vivado: достигнут предел итераций 10000

Пока я пытался запустить симуляцию в vivado, я получил:

ОШИБКА: достигнут предел итераций 10000. Обнаружены возможные колебания с нулевой задержкой, когда время моделирования не может увеличиться. Пожалуйста, проверьте свой исходный код....

31.10.2023

Неподключенные порты - ошибка Verilog Synthesis

Я синтезирую свой RTL, но продолжаю получать сообщение об ошибке. Предупреждение: в дизайне «DasisyChain3» порт «m1_data[7]» не подключен ни к каким цепям (LINT-28). Я не уверен, почему он говорит мне это. Я включил все модули в свой проект, который...

24.12.2023

Новые материалы

Кластеризация: более глубокий взгляд

Кластеризация — это метод обучения без учителя, в котором мы пытаемся найти группы в наборе данных на основе некоторых известных или неизвестных свойств, которые могут существовать. Независимо от..

Как написать эффективное резюме

Предложения по дизайну и макету, чтобы представить себя профессионально

Вам не позвонили на собеседование после того, как вы несколько раз подали заявку на работу своей мечты? У вас может..

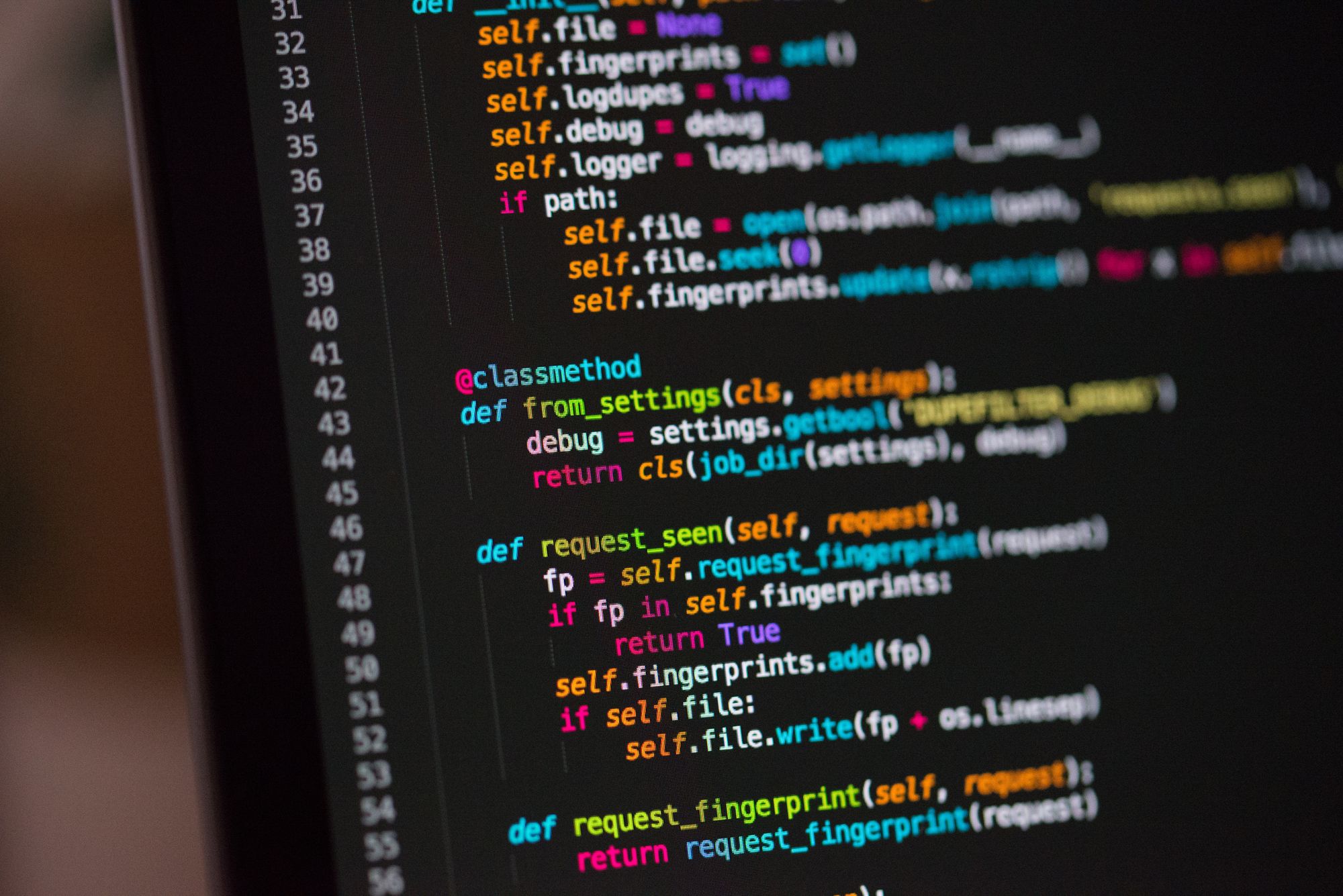

Частный метод Python: улучшение инкапсуляции и безопасности

Введение

Python — универсальный и мощный язык программирования, известный своей простотой и удобством использования. Одной из ключевых особенностей, отличающих Python от других языков, является..

Как я автоматизирую тестирование с помощью Jest

Шутка для победы, когда дело касается автоматизации тестирования

Одной очень важной частью разработки программного обеспечения является автоматизация тестирования, поскольку она создает..

Работа с векторными символическими архитектурами, часть 4 (искусственный интеллект)

Hyperseed: неконтролируемое обучение с векторными символическими архитектурами (arXiv)

Автор: Евгений Осипов , Сачин Кахавала , Диланта Хапутантри , Тимал Кемпития , Дасвин Де Сильва ,..

Понимание расстояния Вассерштейна: мощная метрика в машинном обучении

В обширной области машинного обучения часто возникает необходимость сравнивать и измерять различия между распределениями вероятностей. Традиционные метрики расстояния, такие как евклидово..

Обеспечение масштабируемости LLM: облачный анализ с помощью AWS Fargate и Copilot

В динамичной области искусственного интеллекта все большее распространение получают модели больших языков (LLM). Они жизненно важны для различных приложений, таких как интеллектуальные..