Я пытаюсь написать конечный автомат на VHDL, который будет сканировать клавиатуру 4x4. Я хочу, чтобы keyP был установлен на 0 в начале и после сброса. Я также хочу, чтобы Col было установлено на «1111» в начале и после сброса.

Поскольку я не полностью разбираюсь в программировании VHDL, я уверен, что это просто глупая синтаксическая ошибка.

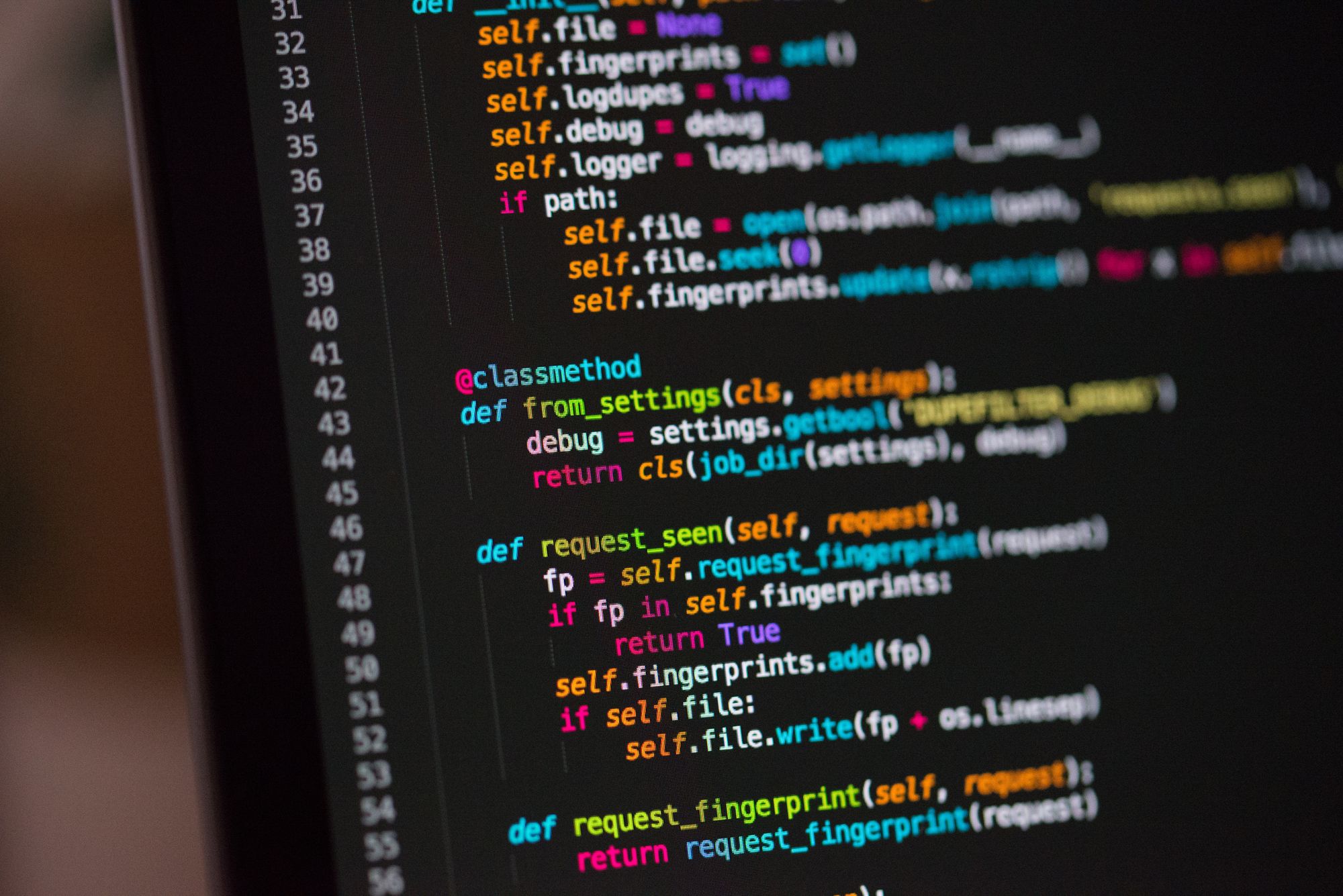

Я получаю следующую ошибку:

Ошибка (10818): невозможно вывести регистр для «Col[0]» в Lab_7_Keypad.vhd(39), так как он не удерживает свое значение за границей тактового сигнала.

и то же самое для Col[1], Col[2], Col[3], а также для keyP.

Вот мой код для начала всего этого. Может ли кто-нибудь дать мне представление, где я ошибся?

Спасибо

ENTITY Lab_7_Keypad IS

PORT(

nReset : IN STD_LOGIC;

clk : IN STD_LOGIC;

row : IN STD_LOGIC_VECTOR (3 downto 0);

Col : OUT STD_LOGIC_VECTOR (3 downto 0);

data : OUT STD_LOGIC_VECTOR (3 downto 0);

keyP : OUT STD_LOGIC);

END Lab_7_Keypad;

ARCHITECTURE a OF Lab_7_Keypad IS

TYPE STATE_TYPE IS ( Col1Set, Col2Set, Col3Set, Col4Set );

SIGNAL coltest : STATE_TYPE;

BEGIN

PROCESS (clk, nReset )

BEGIN

keyP <= '0';

Col <= "1111";

IF nReset = '0' THEN -- asynch Reset to zero

coltest <= Col1Set;

Col <="1111";

keyP <= '0';

ELSIF clk'EVENT AND clk = '1' THEN -- triggers on PGT

CASE coltest IS

WHEN Col1Set =>

Col <="1110";

CASE row IS

WHEN "1110"=>--row 1

data <= "0001";

keyP <= '1';

WHEN "1101"=>--row 2

data <= "0100";

keyP <= '1';

WHEN "1011"=>--row 3

data <= "0111";

keyP <= '1';

WHEN "0111"=>--row 4

data <= "1110";

keyP <= '1';

WHEN OTHERS => coltest <= Col2Set;

END CASE;

--And continues with same Case statements three more times.